C to RTL with H/W Expert

概要

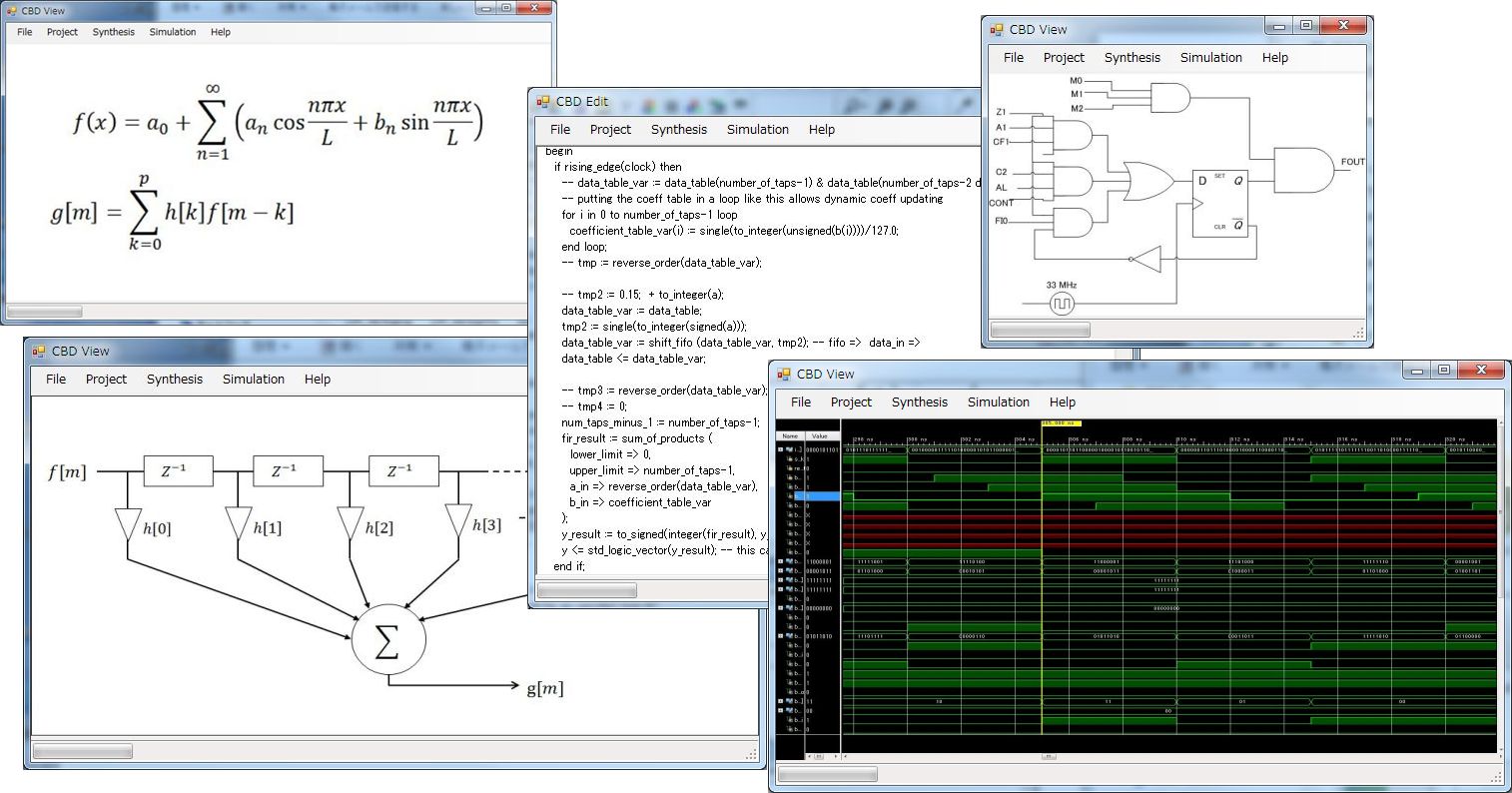

C/C++等で記述されたアルゴリズム・ソース、もしくはアルゴリズム仕様書(数式)よりHDL記述を行い、ハードウェア設計を行うソリューションです。

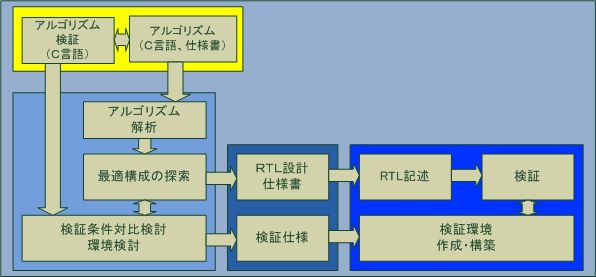

従来のハードウェア設計は主に完成されたハードウェア実装仕様書に基づいてHDLを記述していましたが、本ソリューションではアルゴリズム・ソースを使用して解析を行い、ハードウェア向け構成検討、最適化探索、実装仕様書作成、HDL 記述、検証環境構築までをまとめて行います。

アルゴリズムをハードウェアに実装する場合にハードウェアの設計経験がない、もしくは、経験を持つ技術者を割り当てられない場合や、ハードウェア実装に際しSystemC等の高位合成言語で合成および最適化が困難な場合、アルゴリズム開発側でHDL言語の開発環境を使用できない場合にも対応します。

特長

アルゴリズムのハードウェア実装をHDL言語で行う過程において、当社エンジニアの設計スキルと設計工程管理により品質を確保します。

1. アルゴリズムの解析

提供されたC言語およびアルゴリズム仕様書の構成内容を解析します。C言語で行うため、アルゴリズム開発者との相互検討が効率的に行えます。

1)最適化のための構成解析

2)データ処理のための精度検討

2. 最適化構成の探索

必要に応じて、解析結果で得られた構成を元にハードウェアの実装構成を作成し、最適な構成を探索します。実装構成はC言語で行われるので、アルゴリズムの継承状況をアルゴリズムの開発者と確実に相互検討できます。

1) ソフトウェアの機能分割と性能検討

2) データ処理と制御回路の構成

3) 回路規模

4) 消費電力

5) 動作速度

3. 実装向け検証環境の検討

データ処理はアルゴリズム開発時に用いられる浮動小数点演算をハードウェアで実装可能な精度へ変更します。C言語でアルゴリズムの検証環境を作成し、HDL記述でも使用することで、アルゴリズム開発者との確認を容易かつ確実にします。

1) ハードウェア実装される構成と演算精度の検討

2) 精度検証環境のハードウェア設計検証環境への導入

4. ハードウェア実装に向けた仕様作成

HDL記述を行うための仕様書を検討結果から作成します。

1) 決定したハードウェア構成での実装仕様の作成

2) 検証仕様書作成

5. HDL記述

仕様書を元にHDLの記述を行います。

1) 仕様書からのHDL記述

2) 検証環境の導入

6. 設計検証

C言語からの検証環境を継承し、HDL言語で記述されたアルゴリズム実装を検証します。

7. 実機検証

画像データなどの大容量、高速の処理で必要な実機での検証をFPGAへ実装し、行います。

資料ダウンロード

![]() SystemC 設計ソリューション

SystemC 設計ソリューション![]()

![]() C Based Design Solution

C Based Design Solution![]()

関連ソリューション・サービス

お問い合わせ

東京都渋谷区南平台町2-15

Tel : 03-4335-2610 Fax : 03-4335-2651

E-mail:Embedded-Info@ml.nsw.co.jp