C to FPGA with SystemC/C/C++

概要

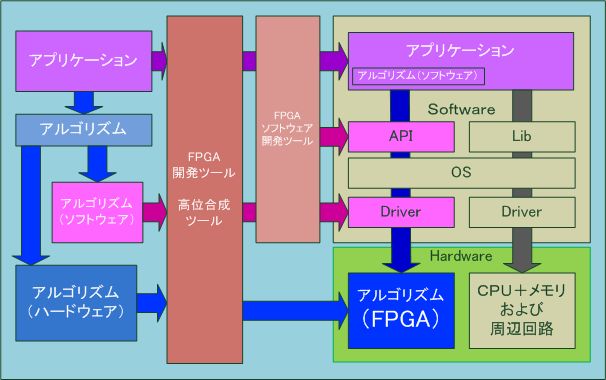

FPGAデバイスの論理回路設計に高位合成言語(SystemCその他)を使用し、機能を実現するアルゴリズムのハードウェアへの実装と組み込みアプリケーション・ソフトウェア開発環境を統合するソリューションです。

FPGAデバイスを使用するハードウェア設計ではハードウェア記述言語(VHDL,Verilog,その他FPGA専用言語)が用いられていますが、複雑化するアルゴリズムを効率よくハードウェアへ実装する手段として、要求が増している高位合成言語(SystemCもしくはハードウェア向けC言語)の使用およびソフトウェアライブラリのハードウェア化を実現します。

FPGA実装に高位合成言語を使用するメリット

機能を実現したアルゴリズムのハードウェアへの実装は、一般的にC言語もしくは実装仕様書に基づいてFPGA用のHDL言語で行われます。ハードウェア向けの構成でC言語によりアルゴリズムを記述している場合はFPGAへの実装、つまりHDL言語への書き換えが比較的容易ですが、アルゴリズムおよびソフトウェアとハードウェアの設計について一人の技術者が熟知している必要があります。

しかし、高度な処理を行うアルゴリズムは複雑かつソースコードが大きくなる傾向にあり、またハードウェアへの実装をアルゴリズム開発初期段階から考慮することは非能率的なため、ソフトウェアとハードウェアは別々の技術者で分担する必要があります。高位合成言語(SystemCもしくはC類似ハードウェア記述言語)を使用したアルゴリズムのFPGAへの実装は、HDL言語への書換えが不要で、ソフトウェア技術者とハードウェア技術者の直接的連携を支援し効率化します。

複雑化する機器は、高度なアルゴリズムをソフトウェアとハードウェアに機能分割し実装することで、ハードウェア規模の最適化および低消費電力と高速処理を実現しています。高位合成言語を使用することにより、機能分割および構成を柔軟に修正でき、目的性能に合わせた最適化を容易にします。

ソリューションの特長

1. ソフトウェア技術とハードウェア技術の連携

アルゴリズム開発から実装までソースコードを継承し、FPGAの特長である製品の柔軟な改善およびアルゴリズムからの修正を迅速にします。

1) ソフトウェア技術者とハードウェア技術者の開発環境の共有

2) 高位合成言語によるアルゴリズムのソースコードの継承

SystemCもしくはC類似言語により実装後のアルゴリズム改善が可能に

3) ソフトウェア側からのインターフェースの明確化とハードウェア実装の分離

異なる実装ノウハウの活用が可能に

2.高位合成言語(ハードウェア記述言語)への書き換え

ハードウェア実装であるアルゴリズム記述のC/C++言語から高位合成言語への書き換えは、ハードウェア実装に必要なスキルを有する技術者が行うため、アルゴリズム開発時の考慮は少なくて済みます。

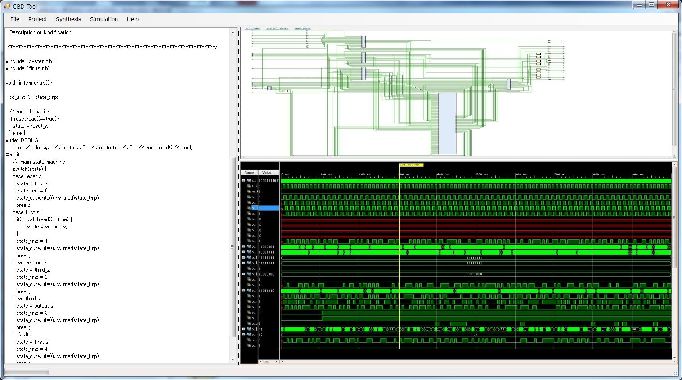

1) SystemC -大規模な回路開発を回路シミュレーター等のEDAツールで効率的に開発

2) C類似ハードウェア記述言語 -FPGA専用開発ツールに向けにソフトウェアとの最適化が容易

3. SoC型FPGAによる設計

CPUを内蔵するSoC型のFPGAでは、ソフトウェア開発とハードウェア開発が一体化され、開発ツールも統合されます。本ソリューションでは統合された開発ツール上へアルゴリズムを実装するために必要となる設計を提供します。

1) アルゴリズムのソフトウェアとハードウェアのパーティショニング最適化

2) アルゴリズムのハードウェア実装

3) ハード化されたアルゴリズムモジュールを使用するためのドライバおよびライブラリ開発

4) OS環境の実装支援

4.ベンダツールによる効率化

1) 規模が大きいハードウェアを実装する場合は、SystemCによるEDAベンダの高位合成ツールの使用を推奨します。

EDAベンダの専用ツールの使用により、大規模回路の検証を効率化でき、シミュレーションでの詳細な設計検証が可能になります。

2) FPGAベンダの専用ツールの環境にも対応します。

FPGAベンダのツールの使用により、実機での開発と検証を効率化できます。

実装例

1.オープンソース・ソフト(OpenCV)の実装例

オープンソースの画像処理ライブラリであるOpenCVのコーナー検出(CornerHarris)をSystemCへ書き換えてFPGAに実装し、リアルタイム処理を実現しています。CソースコードからFPGAの論理回路に実装しており、ソフトウェア処理はありません。

>>C to RTL with SystemC 設計フローとオープンソース・ソフトの実装例

2.画像処理(霞除去 HazeReduction)の実装例

当社のハードウェアIP製品(霞除去「HazeReduction」)をFPGAに実装した例になります。HazeReductionアルゴリズムをCPU内蔵FPGAのハードウェア環境へ実装し、OS(Linux)の動作環境へドライバとアプリケーションを追加して動作させています。

>>画像鮮明化「HazeReduction」FPGA画像処理

資料ダウンロード

![]() SystemC 設計ソリューション

SystemC 設計ソリューション![]()

![]() C Based Design Solution

C Based Design Solution![]()