C to RTL with SystemC 設計フローとオープンソース・ソフトの実装例

概要

コンピュータービジョンに広く普及しているOpenCVのCornerHarrisをハードウェア化した実装例を紹介します。

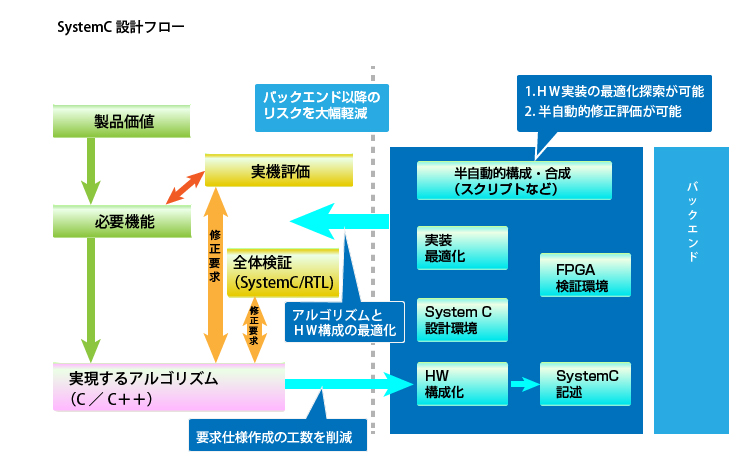

SystemC 設計フロー

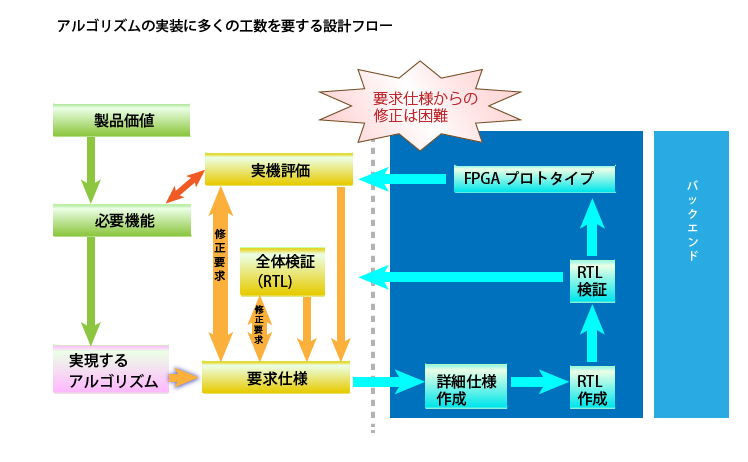

1.従来(RTLベース)設計フローと課題

既存のRTLを使用したハードウェア実装設計は、ハードウェアに切出す部分の「実装仕様」をもとに、RTLの振る舞いを設計した「詳細設計」に基づき設計されます。

製品価値を決定するアルゴリズムからスタートする設計では下表のような課題がありました。

SystemCを使用するソリューションはアルゴリズム・ソースもしくはアルゴリズム仕様から直接ハードウェア設計を行い、これらの課題を解決します。

| 主な課題 (RTLによる回路設計) | 主な課題に対する解決策 (SystemCを使用する場合) | |

| 1 | 実装仕様は、アルゴリズムから自然言語で再作成する必要がある。 | 実装仕様書の作成を取りやめ、作成にともなう誤解、誤記のリスクを回避できる。 |

| 2 | 回路設計は、実装仕様に基づきRTL言語で開発される。そのため、アルゴリズム開発者には理解が難しい。 | ハードウェア実装技術者とアルゴリズム開発技術者双方で理解できるSystemCの使用により、親密な連携を実現できる。 |

| 3 | デバイス構成上でRTLのシミュレーションにより評価する。ただし、実行速度が極めて遅く、機能の評価はほぼ不可能。 | SystemCではRTLサイクルベースシミュレーションとは別に、機能シミュレーションを高速に実行し、アルゴリズム開発者が実装時の機能を評価可能となる。 |

| 4 | バックエンド設計後に作成するESチップを実機上で評価するため、事後評価となり、デバイス作成のリスクが大きい。 | バックエンド設計以前にFPGAでの評価をアルゴリズム開発者を含めて行うことで、デバイスの再作成のリスクを軽減できる。 |

| 5 | アルゴリズム開発者がハードウェアの制限を理解してコードを作成することは困難であり、効率が低下する。 | アルゴリズム開発者にも理解可能なソースコードにアルゴリズムに直接関与しないI/F回路の付加およびハードウェア構成化を行うことで、回路設計に係るリソースとスキル、経験を提供できる。 |

2.SystemC設計フローによる解決

アルゴリズム開発者とハードウェア設計者の直接的協調によって、製品開発と評価を並行して行います。

想定されるニーズ

(1)ハードによる高速化

開発中もしくは保有しているC/C++ベースのアルゴリズムをハードウェアで処理し、機器の性能を上げたい。

(2)実機での評価・改善

アルゴリズムの開発を実機環境(FPGA)で評価・改善を行い、製品ではデバイスでの実装を必要としている。

(3)回路設計の効率化

ハードウェア開発部門において、C/C++言語によるアルゴリズムを迅速にデバイスへ実装したい。

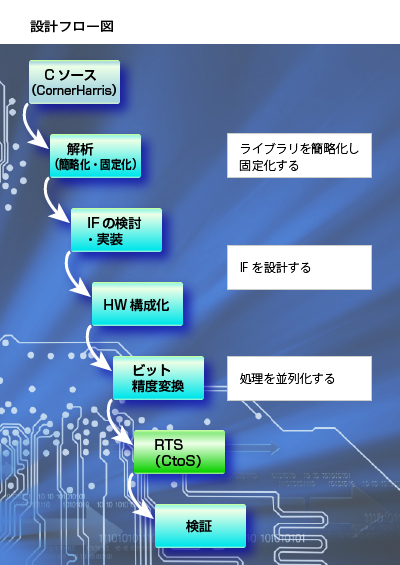

OpenCVのSystemC設計フローによる実装例

1.アルゴリズム解析

オープンソースは汎用的であり、さまざまな用途に対応できるよう記述されています。

基本的にはソフトウェアですのでハードウェアでの実装は考慮されていません。

はじめにハードウェア実装を可能にするためにソフトウェア技術者による解析と、ハードウェア技術者による簡略化および固定化を分担して実施します。

2. SystemC記述への修正、追記

H/W構成化で入出力I/Fを設計します。

(1)クラスや関数(Mat,Filter)をCornerHarris専用に修正

同時にフィルターのカーネルサイズを固定化。

(2)メモリ使用を最低限にするためにラインバッファを使用する処理に変更

(3)パイプライン化で高速処理

(4) 式を変形し乗算器の演算ビット数を調整

3.アルゴリズム修正の結果確認

CornerHarrisの例ではSystemC記述へ修正し、FPGAで実機の動作検証を行いました。実機検証において動作上の問題が発生しましたが、SystemCソースの使用でソフトウェア技術者とハードウェア技術者が一緒に結果を検討し、効率的にソースの修正ができました。

高位合成ツールを使用する環境構築後は、ソース修正による結果をFPGA実機へ即時に展開し、再度評価を実施することで問題点を解決しました。

ハードウェア構成の変更と最適化

(1)表示のずれ

タイミング使用の修正。

(2)パイプラインの段数調整

RTL設計では仕様変更に該当し、柔軟に変更が困難。

(3)演算式を変形し、動作速度と回路規模を縮小

※いずれも、仕様書に沿った設計フローでは修正は仕様書の更新から行うため、相当の期間を必要とします。

このため、通常の場合、修正の実施は、期間・修正項目数・機能への影響度その他の判断に基づき限定されます。

デモ動画

上記の設計フローによりOpenCV CornerHarrisをFPGAボード上で動作させています。リアルタイム処理を実現し走行中の車両のコーナー検出が可能です。また、閾値の変更も即時に反映されています。