C Based Design Solution

概要

半導体製造技術の進歩は大規模回路の実装を可能にし、規模がますます拡大しています。

一方、製品に実装される機能は複雑化し、処理を決めるアルゴリズムからのハードウェア設計要求も増しています。

このため、開発中のアルゴリズムの精度を、保ちながら効率よく大規模なハードウェアに実装する新たな手法が求められます。

従来の回路設計は、主に実装仕様書に基づきHDL記述を行っており、仕様書はアルゴリズム側とハードウェア側で個別に作成されています。そのため、設計効率が悪く、演算精度の維持もハードウェアの専門性と経験が必要でした。

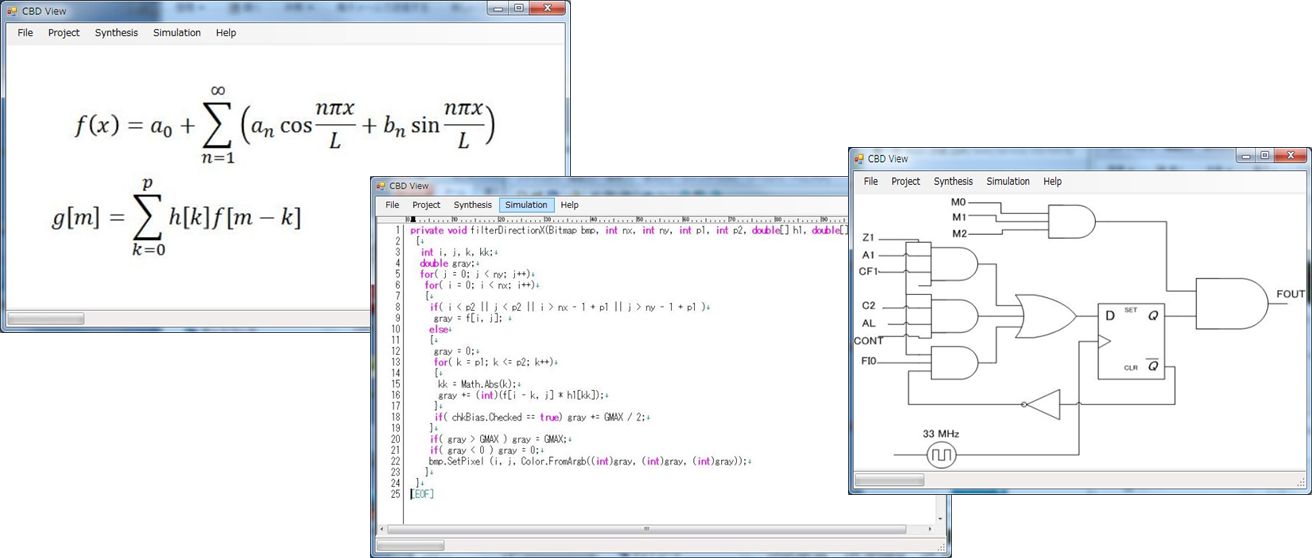

当社ではアルゴリズム・ソースコード(C/C++言語)またはアルゴリズム仕様書から直接ハードウェア設計を行うソリューションを提供し、以下を実現します。

■アルゴリズムの継承性維持と設計の効率化

■ソフトウェア・エンジニアとハードウェア・エンジニアの専門性の活用と協調

SystemC Design Service 「C to RTL with SystemC」

従来手法から進化、アルゴリズムからハードウェア化するメリット

ハードウェア設計にSystemC記述を使用し、アルゴリズム開発者とハードウェア設計者の直接的な協調により、アルゴリズム開発と製品開発および評価を並行して行います。

>> C to RTL with SystemC ソリューションの詳細

C to FPGA with SystemC/C/C++

FPGA用専用ツールでアルゴリズムをFPGAにマッピング

ソフトウェア処理とハードウェア処理のトレードオフを検討。アルゴリズム・ソースからのハードウェア向けのSystemC/C/C++またはC類似高位合成言語を作成し、FPGA専用ツールで実装します。

C to RTL with H/W Expert

ツールでのRTL生成が困難なアルゴリズムでも、技術者がRTL化

高位合成ツール(HLS)の制限や開発環境・リソース要因で問題がある場合でも、アルゴリズム・ソースコードからRTLでアルゴリズムのハード実装を行います。

>> C to RTL with H/W Expert ソリューションの詳細